ATmega32 Timer 1 Phase Correct PWM Mode

Dieses Programm ist ein Sourcecode Example für den Phase Correct PWM Mode mit dem Timer 1 des ATmega32.

|

Beschreibung

Der Timer1 läuft im Phase correct PWM Mode. An PD5 wird das PWM Signal ausgegeben. Die Overflow- und Compare Interrupts

sind eingeschaltet und ihr Auftreten wird auf den Kanälen PA0 und PA1 angezeigt.

Bei jedem Interrupt, erscheint auf dem zugehörigen Digitalport ein Puls. Das PWM Signal hat einen Dutycycle von 10%. |

Please visit: the four |

C Sourcecode

#include <avr/io.h>

#include <avr/interrupt.h>

int main(void)

{

DDRD = 0x20; // Setup PD5 as output

DDRA = 0x03; // Setup PA0 and PA1 as output

ICR1 = 1000; // Set TOP to 10000

OCR1A = 100; // Set Dutycycle to 10%

TCCR1A = (1<<WGM11)|(1<<COM1A1); // Set Timer1 in Phase Correct Mode

// with ICR1 as TOP value. Set OC1A

TCCR1B = (1<<WGM13)|(1<<CS10); // on compare match and clear OC1A

// on BOTTOM. Clock Prescaler is 1024

TIMSK |= (1<<TOIE1) | (1<<OCIE1A); // Enable Timer 1 Overflow

// and Compare interrupt

sei(); // Set the I-bit in SREG

for(;;); // Endless loop

// main() will never be left

return 0; // This line will never be executed

}

// Interrupt subroutine timer 1 overflow

ISR(TIMER1_OVF_vect)

{

PORTA ^= 0x01; // Toggle PA0

PORTA ^= 0x01; // Toggle PA0

}

// Interrupt subroutine timer 1 compare A match

ISR(TIMER1_COMPA_vect)

{

PORTA ^= 0x02; // Toggle PA1

PORTA ^= 0x02; // Toggle PA1

}

Download lauffähiges C-File mit ASCII-Schema: Downloadlink

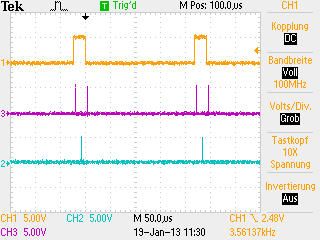

Signalplots

|

Gelb: PWM Ausgangssignal PD5 (OC1A)

|