ATmega8 Timer1 Phase Correct PWM

dieses Programm betreibt den Timer1 im Phase Correct PWM Mode und zeigt Overflow und Compare Zeitpunkte an.

|

Beschreibung Dieser Code für den ATmega8 Timer1 PWM arbeitet mit dem Phase correct PWM Mode. Der Ausgang PC0 zeigt die Zeitpunkte des Overflows an, der Ausgang PC1 die Zeitpunkte der Compare Matches, wo das PWM signal umschaltet. Diese bieden Ausgänge werden in ihren Interruptroutinen umgeschaltet. Das PWM Signal selber ist am Ausgang PB1 (OC1A) ist das PWM Signal abgreifbar. |

Please visit: the four |

C Sourcecode

#include <avr/io.h>

#include <avr/interrupt.h>

int main(void)

{

DDRB = 0x02; // Setup PB1 as output

DDRC = 0x03; // Setup PC0 and PC1 as output

ICR1 = 1000; // Set TOP to 10000

OCR1A = 100; // Set Dutycycle to 10%

TCCR1A = (1<<WGM11)|(1<<COM1A1); // Set Timer1 in Phase Correct Mode

// with ICR1 as TOP value. Set OC1A

TCCR1B = (1<<WGM13)|(1<<CS10); // on compare match and clear OC1A

// on BOTTOM. Clock Prescaler is 1024

TIMSK |= (1<<TOIE1) | (1<<OCIE1A); // Enable Timer 1 Overflow

// and Compare interrupt

sei(); // Set the I-bit in SREG

for(;;); // Endless loop

// main() will never be left

return 0; // This line will never be executed

}

// Interrupt subroutine timer 1 overflow

ISR(TIMER1_OVF_vect)

{

PORTC ^= 0x01; // Toggle Pc0

PORTC ^= 0x01; // Toggle PC0

}

// Interrupt subroutine timer 1 compare A match

ISR(TIMER1_COMPA_vect)

{

PORTC ^= 0x02; // Toggle PC1

PORTC ^= 0x02; // Toggle PC1

}

Download C-Sourcefile mit ASCII-Schema: C-Sourcefile mit ACII-Schema

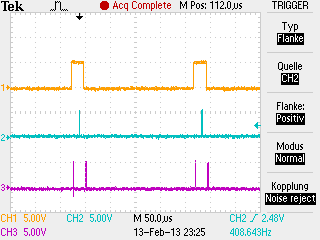

Signalplots

|

Gelb: Digitaler Ausgang OC1A

|